利用NSi810x高(gāo)效快速實現IIC設備隔離

2019-08-22 13:30:00IIC總線結構簡單且易于實現,廣泛應用于設備或模塊間的連接。在某些數據采集和電(diàn)源控制設備中,必須把IIC主設備與一(yī)個(gè)或多(duō)個(gè)從(cóng)設備隔離開(kāi)來,以便解決噪聲、接地、安全等問題。本文主要介紹如何利用納芯微電(diàn)子(NOVOSENSE)生(shēng)産的NSi810x系列芯片高(gāo)效快速的實現IIC設備隔離。

首先我們先來了解下(xià)NSi810x系列芯片。NSi810x系列芯片為(wèi)兼容IIC接口的高(gāo)可靠性雙向數字隔離器(qì),其符合AEC-Q100标準,具有高(gāo)電(diàn)磁抗擾度和低(dī)輻射的特性。NSi810x系列産品的主要性能(néng)指标如下(xià):

l 高(gāo)達5000V隔離電(diàn)壓

l IC時鍾速率:高(gāo)達2MHz

l 供電(diàn)電(diàn)壓範圍:2.5V~5.5V

l 高(gāo)CMTI:150kV/us

l 芯片級ESD:HBM高(gāo)達±6kV

l 高(gāo)系統級EMC性能(néng):增強型系統級抗ESD、EFT、浪湧能(néng)力

l 隔離帶壽命:>60年(nián)

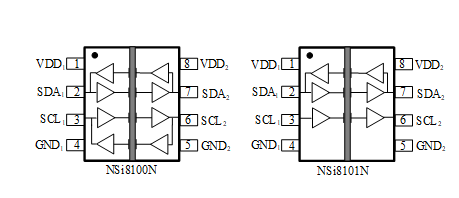

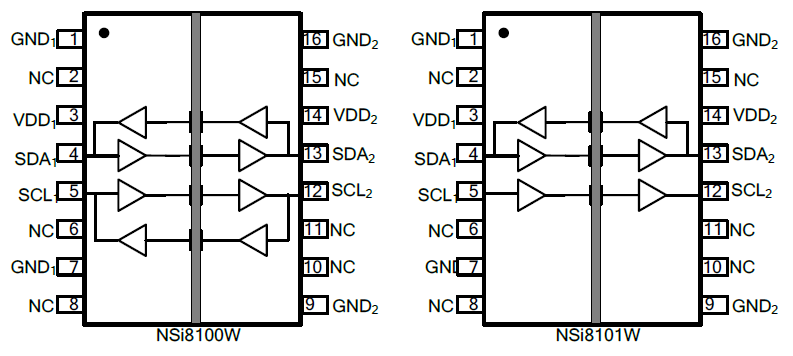

NSi810x系列均包含窄體SOIC8及寬體SOIC16兩種封裝形式,各型号功能(néng)框圖如下(xià):

圖1 NSi8100/01窄體SOIC8封裝圖

圖2 NSi8100/1寬體SOIC-16封裝圖

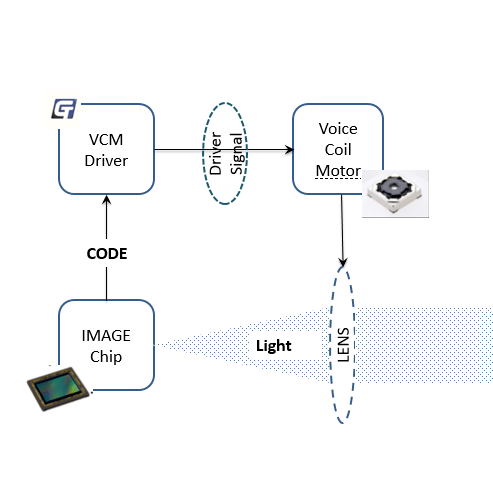

NSi810x系列典型應用電(diàn)路(lù)

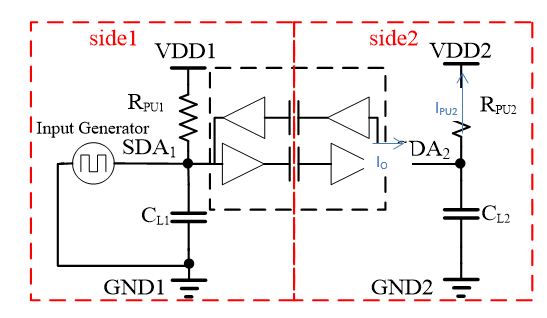

NSi810x系列産品外圍電(diàn)路(lù)簡單,隻需要雙端電(diàn)源供電(diàn)及在IIC通(tōng)信引腳連接上(shàng)拉電(diàn)阻滿足芯片的開(kāi)漏驅動即可實現IIC總線的隔離(如圖3)。那麽,如何選取合适的上(shàng)拉電(diàn)阻,是該類應用電(diàn)路(lù)的關鍵。

分析上(shàng)拉電(diàn)阻對隔離電(diàn)路(lù)的影響時,需要考慮兩種情況。第一(yī)種情況是當SDA傳向SDA的信号由高(gāo)電(diàn)平轉換為(wèi)低(dī)電(diàn)平時(如圖3),必須保證NSi810x的輸出驅動能(néng)力I大于外部上(shàng)拉電(diàn)路(lù)的上(shàng)拉能(néng)力I,SDA的狀态才能(néng)跟随輸入狀态發生(shēng)相(xiàng)應變化。

I=15mA

I≈VDD2/ R

選取最大供電(diàn)電(diàn)壓5.5V的情況, R應滿足如下(xià)條件(jiàn):

當I

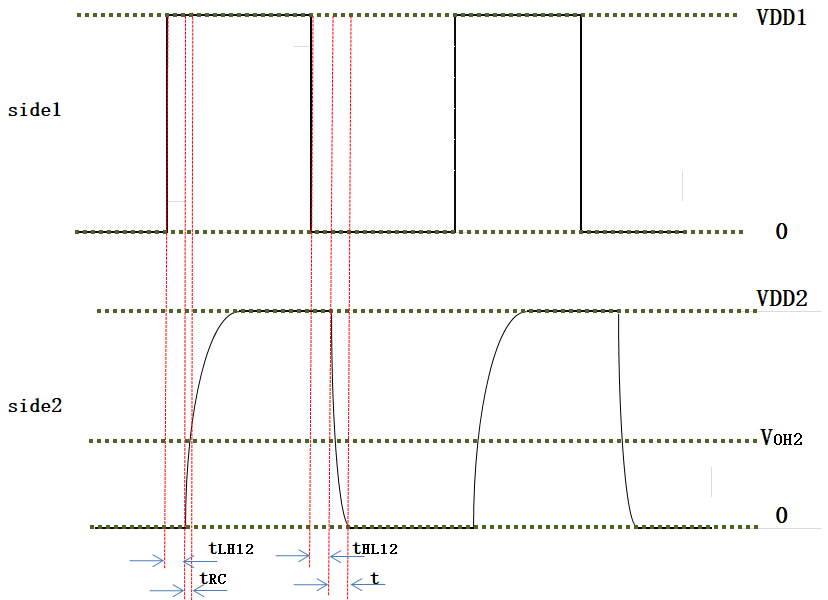

第二種情況是當SDA傳向SDA的信号由低(dī)電(diàn)平轉換為(wèi)高(gāo)電(diàn)平時,由于NSi810x系列的開(kāi)漏驅動特性,SDA的狀态由外部上(shàng)拉電(diàn)路(lù)決定。此外,由于電(diàn)路(lù)中對地負載電(diàn)容與上(shàng)拉電(diàn)組的RC電(diàn)路(lù)的充電(diàn)效應,使得side2輸出恢複高(gāo)電(diàn)平的時間(t)與除了與隔離電(diàn)路(lù)傳播延時(t)有關,還(hái)與該RC電(diàn)路(lù)的充放(fàng)電(diàn)時間有關(t),即

t= t+ t

在相(xiàng)同的負載電(diàn)容情況下(xià),上(shàng)拉電(diàn)阻越大,t 就(jiù)越大,導緻輸出上(shàng)升時間就(jiù)越長(cháng)。又(yòu)由于其下(xià)降時間不随RC的大小(xiǎo)發生(shēng)變化,因此,過大的上(shàng)拉電(diàn)阻可能(néng)會(huì)導緻輸出信号的占空比發生(shēng)改變。當信号速率越高(gāo),信号鏈越長(cháng),該狀況引起的危害越大。

由SDA向SDA發送信号時的狀況與此類似,在此不進行贅述。

圖4 隔離IIC信号傳輸波形

由上(shàng)述可知,在滿足芯片能(néng)夠正常工(gōng)作的前提下(xià),從(cóng)信号完整性的角度來說,上(shàng)拉電(diàn)阻的阻值取得越小(xiǎo)越好。但在系統級應用中,我們還(hái)需要更全面的考慮其帶來的影響。當我們選取的上(shàng)拉電(diàn)阻阻值越小(xiǎo),信号端被驅動低(dī)電(diàn)平狀态時,該電(diàn)阻在系統中消耗的功耗就(jiù)越大。因此,在實際應用中,我們應該在滿足信号有效傳輸的前提下(xià),選取最大的上(shàng)拉電(diàn)阻以減小(xiǎo)功耗。

NSi810x系列實現防闩鎖雙向通(tōng)信的原理

圖5低(dī)電(diàn)平闩鎖電(diàn)路(lù)等效圖

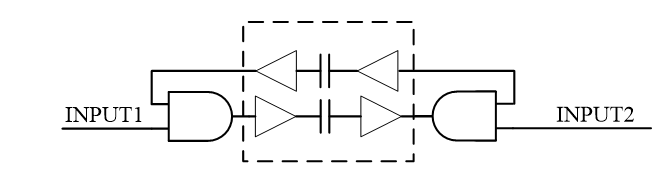

一(yī)個(gè)雙向傳輸的隔離通(tōng)道可利用兩個(gè)反向傳輸的數字隔離通(tōng)道組成。然而,如果單純的将兩個(gè)反向通(tōng)道相(xiàng)連,那麽任何一(yī)端的總線狀态會(huì)由外界輸入和另一(yī)端的傳輸信号相(xiàng)與得到(dào)。當有一(yī)端外界輸入低(dī)電(diàn)平信号時,總線狀态将會(huì)鎖死為(wèi)低(dī)電(diàn)平狀态而無法釋放(fàng),其等效電(diàn)路(lù)狀态如圖5所示。

為(wèi)了解決這種問題,NSi810x在side1端增加内部偏置電(diàn)路(lù),當side2發送低(dī)電(diàn)平信号至side1時,該電(diàn)路(lù)将低(dī)電(diàn)平信号拉高(gāo)至V,對通(tōng)常的COMS或TTL電(diàn)平來說,該電(diàn)壓還(hái)是被判定為(wèi)低(dī)電(diàn)平,但對于NSi810x芯片來說,V在side1端作為(wèi)輸入則會(huì)被識别為(wèi)高(gāo)電(diàn)平傳輸到(dào)side2,從(cóng)而起到(dào)了解除低(dī)電(diàn)平闩鎖的目的。

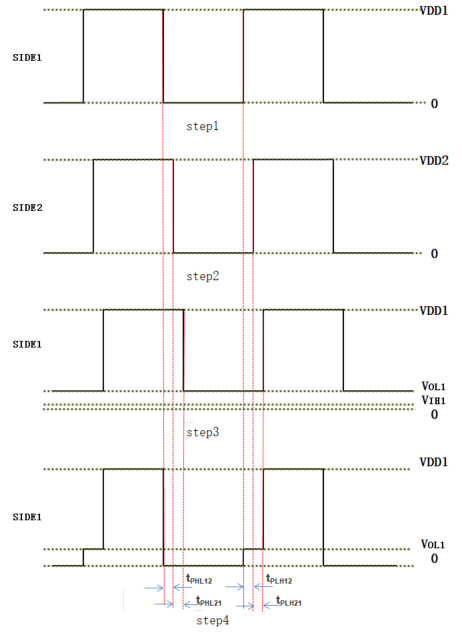

以下(xià)是side1端發送信号電(diàn)平轉換的幾種情況:

I)、side1發送信号由高(gāo)電(diàn)平轉換為(wèi)低(dī)電(diàn)平

l 由外部信号向side1發送低(dī)電(diàn)平信号(step1)

l 經過隔離通(tōng)道的傳播延時時長(cháng)(t),低(dī)電(diàn)平信号傳送至side2(step2);

l 再經過隔離通(tōng)道傳播延時時長(cháng)(t),side2的低(dī)電(diàn)平信号再次回傳至side1(step3)

l side1的實際信号為(wèi)外部輸入信号(step1)與side2回傳的信号(step3)相(xiàng)與。因此,在外部輸入信号由高(gāo)變低(dī)時,實際信号由高(gāo)變低(dī)(step4)。

II)、side1發送信号由低(dī)電(diàn)平轉換為(wèi)高(gāo)電(diàn)平

l 由外部信号向side1發送高(gāo)電(diàn)平信号(step1);

l 經過隔離通(tōng)道的傳播延時時長(cháng)(t), side2端狀态由上(shàng)拉電(diàn)阻拉高(gāo)(step2);

l 再經過隔離通(tōng)道傳播延時時長(cháng)(t),side2的高(gāo)電(diàn)平信号再次回傳side1(step3)

l side1的實際信号為(wèi)外部輸入信号(step1)與side2回傳的信号(step3)相(xiàng)與。因此,當外部輸入信号由低(dī)變高(gāo)時,需經過t+ t時長(cháng)的V才會(huì)再變為(wèi)高(gāo)電(diàn)平信号(step4)。

III)、side2發送信号由高(gāo)電(diàn)平轉換為(wèi)低(dī)電(diàn)平

l 由外部信号向side2發送低(dī)電(diàn)平信号(step2);

l 經過隔離通(tōng)道傳播延時時長(cháng)(t), 低(dī)電(diàn)平信号傳送至side1,由于此時side1信号電(diàn)平V>V,低(dī)電(diàn)平信号不再次進行回傳(step3)。

IV)、side2發送信号由低(dī)電(diàn)平轉換為(wèi)高(gāo)電(diàn)平

l 由外部信号向side2發送低(dī)電(diàn)平信号(step2);

l 經過隔離通(tōng)道傳播延時時長(cháng)(t), side1的狀态由外部上(shàng)拉電(diàn)阻拉高(gāo)至高(gāo)電(diàn)平狀态(step3)

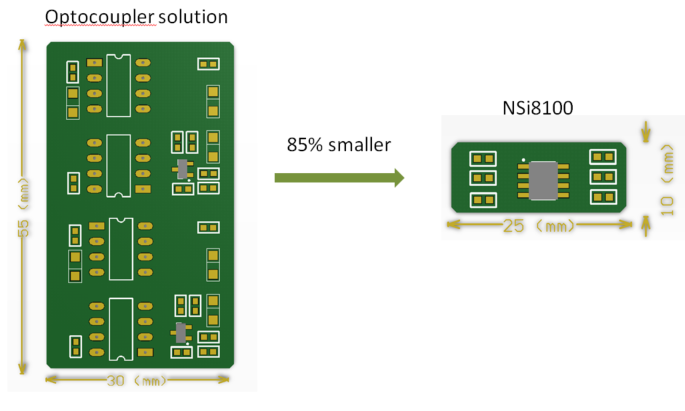

NSi810x VS.傳統光(guāng)耦IIC隔離電(diàn)路(lù)

圖7左側為(wèi)使用4個(gè)光(guāng)耦芯片及複雜(zá)的外圍電(diàn)路(lù)搭建的IIC端口隔離電(diàn)路(lù),其所需器(qì)件(jiàn)産生(shēng)的成本、電(diàn)路(lù)的複雜(zá)度及PCB空間的增加都将大大限制IIC的隔離應用。相(xiàng)比之下(xià), NSi810x僅需單顆芯片及用于電(diàn)源的旁路(lù)電(diàn)容即可實現IIC接口隔離。

圖7 傳統光(guāng)耦IIC隔離電(diàn)路(lù)

圖7 傳統光(guāng)耦IIC隔離電(diàn)路(lù)

除此之外,NSi810x系列芯片的各項功能(néng)指标也遠(yuǎn)優于光(guāng)耦隔離電(diàn)路(lù)(如表1所示)

|

高(gāo)速光(guāng)耦(TLPN137) |

NSi810x |

|

|

傳輸延時 |

75ns |

30ns |

|

隔離電(diàn)壓 |

2500V |

5000V |

|

功耗 |

20mA*4 |

2.5mA*2 |

|

壽命 |

存在光(guāng)衰,壽命短 |

>60年(nián) |

|

溫度範圍 |

-40~85C |

-40~125C |

|

面積 |

55mm*30mm |

25mm*10mm |

|

器(qì)件(jiàn)數 |

28 |

7 |

總結

目前針對市(shì)面上(shàng)不同的應用電(diàn)路(lù)雖然有多(duō)種實現IIC系統隔離的方法,但NSi810x系列集成隔離IIC器(qì)件(jiàn)可實現将SDA與SCL雙路(lù)IIC隔離及其外部電(diàn)路(lù)集成在同一(yī)個(gè)芯片内,使得IIC隔離應用電(diàn)路(lù)更加簡單,且具有速度快、隔離電(diàn)壓高(gāo)、抗共模能(néng)力強、可靠性高(gāo)等優點。此外,NSi810x系列芯片腳對腳兼容目前市(shì)面上(shàng)已有的IIC隔離器(qì)件(jiàn),可幫助工(gōng)程師(shī)以更低(dī)的成本實現高(gāo)性能(néng)的IIC系統隔離功能(néng)。